## Структура аппаратуры ЦОС для синтеза радиолокационного изображения на борту космического аппарата

В.В. Костров, А.Ю. Антонов

Муромский институт (филиал) Владимирского государственного университета имени Александра Григорьевича и Николая Григорьевича Столетовых 602264 г.Муром, Владимирская обл., ул. Орловская, 23. E-mail: <a href="wvk@mit.ru">wvk@mit.ru</a>, <a href="mailto:aleksandr\_uran@mail.ru">aleksandr\_uran@mail.ru</a>

В работе получена структурная схема вычислительной системы синтеза РЛИ трехметрового разрешения на борту низкоорбитального космического аппарата при маршрутном режиме съемки.

The block diagramme of the computer system of synthesis radar image of the three meter resolution is in-process gained onboard the low orbit space vehicle at a stripmap mode.

Получение радиолокационного изображения (РЛИ) сопряжено с большими вычислительными затратами, что требует быстродействующей аппаратуры. Это требование особенно критично для систем, работающих в режиме реального времени. Жесткие условия космического пространства, в частности радиационные воздействия, возможности применяемых ограничивают вычислительных средств, радиоголограммы передаются непосредственно на Землю, где происходит их обработка. Однако пропускной способности радиолиний, как правило, недостаточно для передачи информации, что приводит к периодичности работы радиолокаторов с синтезированной апертурой (РСА), либо ухудшению пространственного разрешения. Применение адаптивного квантования и сжатия данных не позволяют полностью решить эту проблему. Растущая актуальность оперативного наблюдения и развитие технологий приводит к мысли о переносе вычислителя на борт космического аппарата. Это позволит получать изображение в режиме реального времени и максимально использовать возможности РСА.

*Цель данной работы* — разработка структурной схемы вычислительной системы для обеспечения синтеза РЛИ высокого разрешения на борту низкоорбитального космического аппарата при маршрутном режиме съемки.

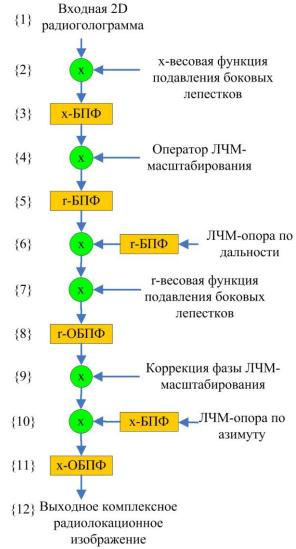

Рассмотрим требования по быстродействию вычислительной системы при маршрутном режиме съемки. В [1] для синтеза РЛИ используется алгоритм, приведенный на рис. 1. Он совмещает в себе алгоритмы быстрой свертки и ЛЧМ-масштабирования для коррекции искажений. В фигурных скобках указаны номера производимых операций. Вычисление опорной функции по дальности и её дальнейшее преобразование по алгоритму БПФ  $\{6\}$  происходит в момент синтеза зондирующего сигнала и на защитном интервале. Вычисление опорной функции по азимуту и её дальнейшее преобразование по алгоритму БПФ  $\{10\}$  происходит до начала обработки радиоголограммы, остальные функции в процессе обработки не изменяются. Таким образом, все необходимые для синтеза данные хранятся в ОЗУ.

Далее производится обработка по строкам дальности: БПФ {5}, умножение на опорную функцию {6} и весовую функцию подавления боковых лепестков {7}, ОБПФ {8}. После чего снова производится обработка по азимуту: коррекция фазы ЛЧМ-масштабирования {9}, умножение на опорную функцию {10} и ОБПФ {11}. Результатом вычислений является комплексное радиолокационное изображение {12}, готовое для конечной обработки и передачи на землю. При этом в алгоритме можно выделить три основных этапа, в рамках которых все операции выполняются последовательно:

- 1) операции {2} {4} обработка по азимуту;

- 2) операции  $\{5\} \{8\}$  обработка по дальности;

- 3) операции  $\{9\} \{11\}$  обработка по азимуту.

Рис. 1. Алгоритм обработки РЛИ в маршрутном режиме

Особенность алгоритма в том, что последующий этап не может начаться после полного завершения предыдущего, это связано с переходом от обработки по азимуту к обработке по дальности и наоборот. Поэтому в данном случае последовательное выполнение операций увеличивает требования к быстродействию системы, так как отсчеты (матрицы) сигналов могут обрабатываться только друг за другом.

Перейдем к выбору аппаратной реализации операций. Поскольку необходимо обеспечить максимальное быстродействие БПФ целесообразно выполнить на программируемой логической интегральной схеме (ПЛИС), поскольку они обладают явным преимуществом во времени преобразования по сравнению с процессорами цифровой обработки сигналов (ПЦОС). Кроме того, ПЛИС позволяют создавать несколько вычислительных блоков внутри одной микросхемы, что улучшает массогабаритные показатели. Остальные операции (имеющие в своей основе комплексное умножение) лучше реализовать на ПЦОС, так как они приспособлены для последовательных вычислений: обладают многоступенчатым конвейером, поддерживают SIMD режим, могут содержать несколько DSP-ядер и значительно проще в написании программы обработки.

Существует множество вариантов реализации блока БПФ (ОБПФ) на ПЛИС. Однако по своей сути они имеют сходные механизмы функционирования и управления. Рассмотрим архитектуры вычислителей по алгоритму БПФ, предлагаемые фирмой Altera: streaming, variable streaming, buffered burst, burst. Они способны выполнять как прямое, так и обратное БПФ. В [2] приведены основные параметры и особенности функционирования.

Сравним данные архитектуры. По количеству используемых логических ячеек, DSP-блоков и производительности архитектуры streaming и variable streaming имеют явное преимущество, особенно первая. Единственное преимущество архитектур buffered burst и burst – объем используемой памяти, для последней он в 2 раза меньше по сравнению с остальными, по всем другим параметрам они проигрывают, и в дальнейшем рассматриваться не будут. Несмотря на универсальность архитектуры variable streaming она требует более сложного управления, имеет худшее время преобразования и большое расширение потока данных – 2,5 бита на каждую ступень БПФ (по основанию бабочки-4). Таким образом, наиболее подходящей для реализации является архитектура streaming.

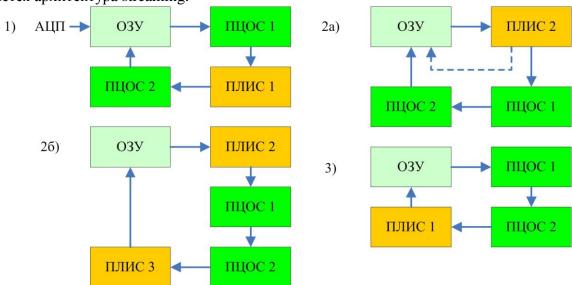

Рис. 2. Обработка сигналов и формирование РЛИ в вычислительных блоках

В соответствии с этапами алгоритма, выбранной архитектурой БПФ и аппаратной реализацией получаем следующий механизм обработки (рис. 2). Считаем, что разные блоки БПФ реализованы в отдельных ПЛИС. Поскольку один блок может выполнять как прямое, так и обратное БПФ, на этапе 2 возможно два варианта организации вычислительных процессов:

- а) Этап разбивается на два подэтапа (общее количество становится 4), однако требуется всего одна ПЛИС, которая выполняет сначала прямое БПФ, затем обратное. Пунктиром на рис. 2 показано прохождение сигнала на втором подэтапе, при этом ПЦОС не задействованы;

- б) Количество этапов не меняется, но требуется две ПЛИС: одна для прямого  $БП\Phi$ , другая для обратного.

С точки зрения максимального быстродействия вариант а) менее предпочтителен, так как требует более высоких тактовых частот примерно на 30% и на втором подэтапе не задействует ПЦОС. Поэтому в дальнейшие расчеты ориентированы на вариант б).

Поскольку вычислительный блок будет применяться в низкоорбитальном спутнике, рассмотрим их типовые параметры в маршрутном режиме съемки. Из таблицы, приведенной в [1] при разрешении 3 м полоса съемки составляет 30 км, что

соответствует 10 тысячам отсчетов дальности. При разрядности данных (мнимой и действительной части) 1 байт, основании БПФ по дальности 16384 и по азимуту 4096, времени синтеза 1 с время обработки отсчета 5 нс. При этом тактовая частота ПЛИС равна 200 МГц. Полученное значение тактовой частоты легко достижимо и имеет некоторый технологический запас. Например, радиационно-стойкие ПЛИС семейства RTAX фирмы Actel способны работать на частотах до 350 МГц [3].

Рассмотрим возможность применения в качестве ПЦОС процессор семейства «Мультикор» МС-0226 (1892ВМ5Я), который содержит в себе 1 RISC и 2 DSP процессора. При максимальной тактовой частоте 100 МГц, 2 DSP-ядрах, 2SIMD режиме и представлении данных 1 байтом он должен выполнять 400 млн. комплексных умножений в секунду. Данное значение производительности соответствует заявленному [4] и в 2 раза превосходит рассчитанные 200 млн. умножений в секунду, то есть данный процессор способен обеспечить требуемую производительность.

На основе полученных результатов рассчитаем скорость потока данных при обработке. Ширина спектра зондирующего сигнала в маршрутном режиме доходит до 75 МГц. Частота дискретизации АЦП в РСА космического базирования выбирается на 10...11 % больше верхней частоты спектра и составляет 83 МГц. При представлении отсчета 2 байтами поток данных на выходе АЦП составит 166 Мбайт/с. В процессе обработки при тактовой частоте 200 МГц поток данных составит 400 Мбайт/с.

Перейдем к выбору интерфейса обмена. Передачу данных от АЦП к вычислительной системе способен обеспечить интерфейс SpaceWire, каждый канал которого обладает дуплексным режимом передачи при скоростях 2...400 Мбит/с (0,25...50 Мбайт/с). SpaceWire поддерживает объединение 4 каналов в так называемый Fat link, который способен передавать 200 Мбайт/с. Обмен данными между вычислительными блоками (ПЛИС и ПЦОС) способен обеспечить интерфейс RapidIO или Link. Однако встроенные в МС-0226 Link порты способны пропустить 70...80 Мбайт/с (итого 280...320 Мбайт/с), что явно недостаточно. Поэтому вопрос о выборе ПЦОС остается открытым.

Общий объем требуемой памяти составляет примерно 552 Мбайт. Данное значение превышает типовое 512 Мбайт на 40 Мбайт, однако следует отметить, что при БПФ размер входного кадра дополняется нулями до ближайшего большего основания. После преобразования эти значения отбрасываются ( $\approx$ 2000 отсчетов). Таким образом, исходный кадр размером  $14K\times2K$  занимает  $14K\times2K\times2$  байта = 56 Мбайт, что экономит 72 Мбайта и позволяет применить типовое значение 512 Мбайт.

Поскольку все данные проходят через ОЗУ, к нему предъявляются повышенные требования по скорости обмена. Условно она состоит из 5 областей для следующих операций: запись исходного кадра (166 Мбайт/с), чтение выходного обработанного кадра (166 Мбайт/с), чтение/запись промежуточных данных (400 Мбайт/с), чтение/запись коэффициентов (40 Мбайт/с). Частично коэффициенты загружаются в ОЗУ при инициализации системы. Суммарная скорость запись/чтение составляет 706 Мбайт/с.

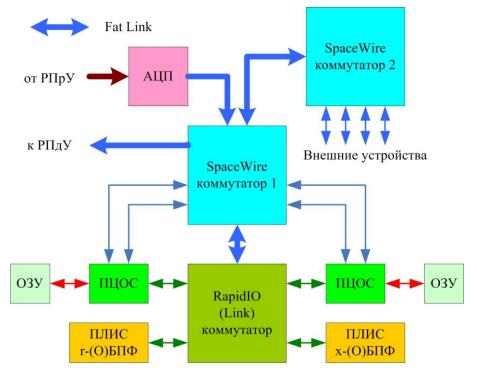

Рис. 3. Структурная схема вычислительной системы

Структурная схема вычислительной системы представлена на рис. 3. На ней приведен вариант с двумя ПЛИС, хотя фактически возможна реализация всех блоков БПФ, а также RapidIO (Link) коммутатора внутри одной ПЛИС. SpaceWire коммутатор 1 обеспечивает основную передачу данных: входной радиоголограммы от АЦП и обработанного РЛИ на радиопередающее устройство. выходного коммутатор 2 необходим ДЛЯ подключения датчиков сбора дополнительной информации, сопровождающей РЛИ.

Таким образом, рассмотренная структурная схема вычислительной системы на основе ПЦОС и ПЛИС позволяет реализовать обработку РЛИ трехметрового разрешения. Данное решение обладает гибкостью и позволяет распределять вычислительную нагрузку между ПЦОС и ПЛИС для получения максимального быстродействия. Сложность реализации данной системы на отечественной элементной базе в основном связана с процессорами, которые имеют недостаточную пропускную способность интерфейсов обмена. обеспечить требуемую но способные производительность. Хотя отечественная промышленность не выпускает радиационностойких ПЛИС с большим числом логических элементов, на основе проектов можно создать базовые матричные кристаллы (БМК), производство которых освоено в России.

## Литература

- 1. Верба В.С., Неронский Л.Б., Осипов И.Г., Турук В.Э. Радиолокационные системы землеобзора космического базирования. М.: Радиотехника, 2010. 676 с.

- 2. FFT megacore function. User guide. v.11.1. Altera, 2011.

- 3. http://www.actel.ru/products/fpga.html#radtolerant

- 4. <a href="http://multicore.ru/index.php?id=46">http://multicore.ru/index.php?id=46</a>