## Глотов Д.А., Жиганов С.Н.

Муромский институт (филиал) федерального государственного образовательного учреждения высшего образования «Владимирский государственный университет имени Александра Григорьевича и Николая Григорьевича Столетовых» 602264, г. Муром, Владимирская обл., ул. Орловская, 23 е-mail: s\_zh\_72@mail.ru

## Построение цифровой системы интерполяции на основе структуры Хогенауэра

Одной из центральных задач, которые решаются в системах цифровой обработки сигналов является разработка систем, обеспечивающих увеличение частоты дискретизации в целое число раз. При этом, как правило, на разработчика подобных систем накладываются дополнительные сложности связанные с реализуемостью системы — уменьшению вычислительной сложности, экономии устройств памяти, уменьшению аппаратной емкости разрабатываемой системы. Для реализации этих дополнительных ограничений были предложены различные подходы к построению систем интерполяции, одна из них - это структура Хогенауэра.

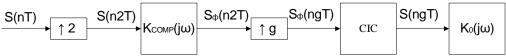

Фильтр-интерполятор на основе аналитической структуры Хогенауэра представлена на рисунке 1.1.

Рисунок 1.1 — Фильтр-интерполятор: каскадное соединение корректирующего FIR-фильтра и CIC-фильтра

Отсчеты входного сигнала поступают на экспандер частоты дискретизации, который увеличивает частоту дискретизации сигнала в два раза путем добавления нулей между каждыми отсчетами сигнала. Далее сигнал поступает на фильтр-корректор, задача которого усилить амплитуду частотных составляющих сигнала, находящихся ближе к частоте среза фильтра.

После фильтра корректора отсчеты сигнала поступают на СІС фильтр, где происходит его фильтрация и увеличение частоты дискретизации в g раз. СІС фильтр первого порядка содержит интегратор и гребенчатый фильтр, но уровень первого бокового лепестка составляет всего лишь –13 дБ, что недопустимо много. Для увеличения подавления в полосе заграждения необходимо использовать СІС фильтры более высокого порядка, полученные каскадным включением нескольких интеграторов и гребенчатых фильтров. Пример структуры СІС фильтра приведена на рисунке 1.2.

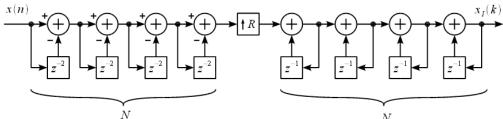

Рисунок 1.2 – Структурная схема модифицированного СІС интерполятора на R-1 отсчетов

Как видно из рисунка 1.2 в структуре фильтра используются только линии задержки и сумматоры, что существенно уменьшает вычислительные затраты на обработку. Кроме этого, к преимуществам подобной структуры можно отнести: - уменьшение вычислительных затрат при реализации на ПЛИС, так как СІС-фильтр не требует операций умножения; - линейная ФЧХ при применении корректирующего FIR-фильтра, который работает на пониженной частоте дискретизации; отмеченная структура является симметричной и может использоваться как в устройствах интерполяции, так и децимации.

К недостаткам рассмотренной структуры можно отнести - увеличение разрядности, которое может вызвать переполнение; - к корректирующему FIR-фильтру предъявляют высокие требование для реализации на ПЛИС, что существенно увеличивает его порядок.